FPGA Design Services

What we do

What’s included

Architecture Development

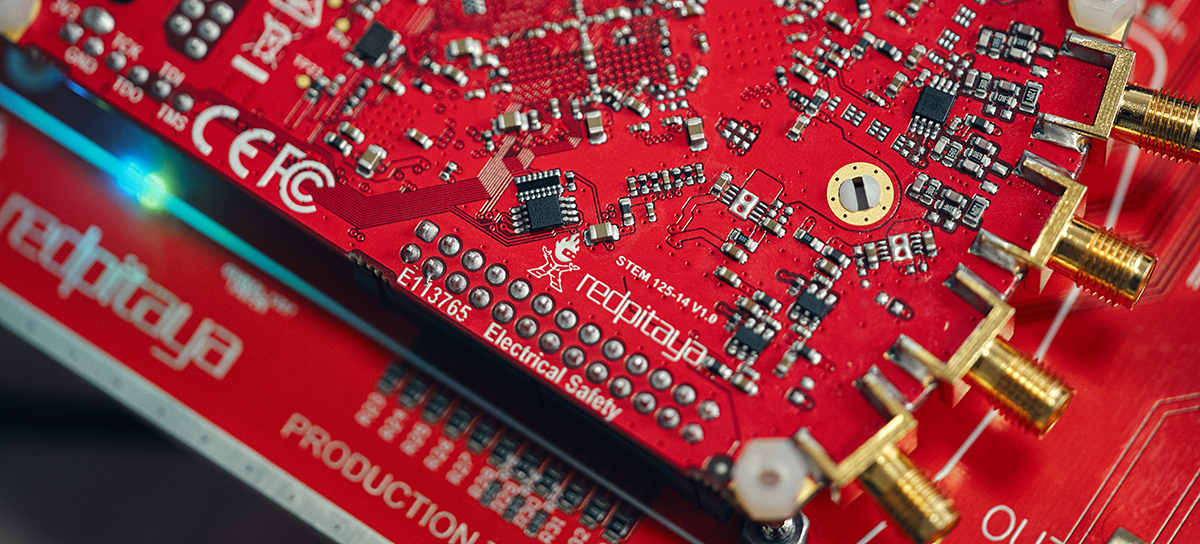

FPGA Design Service

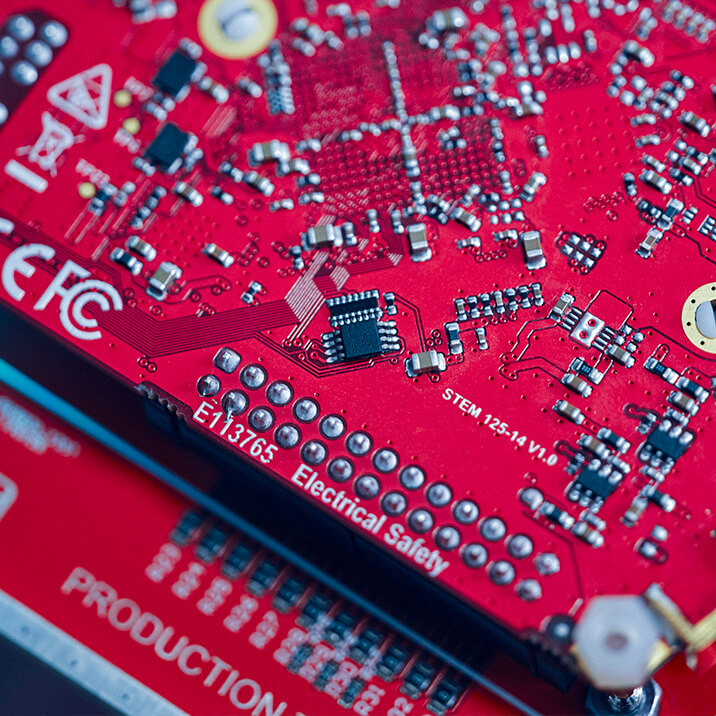

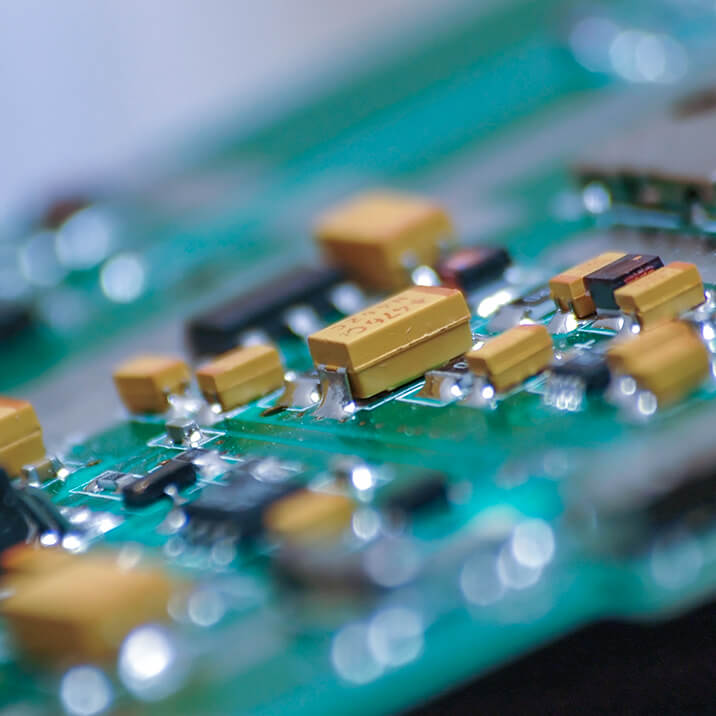

FPGA PCB Design

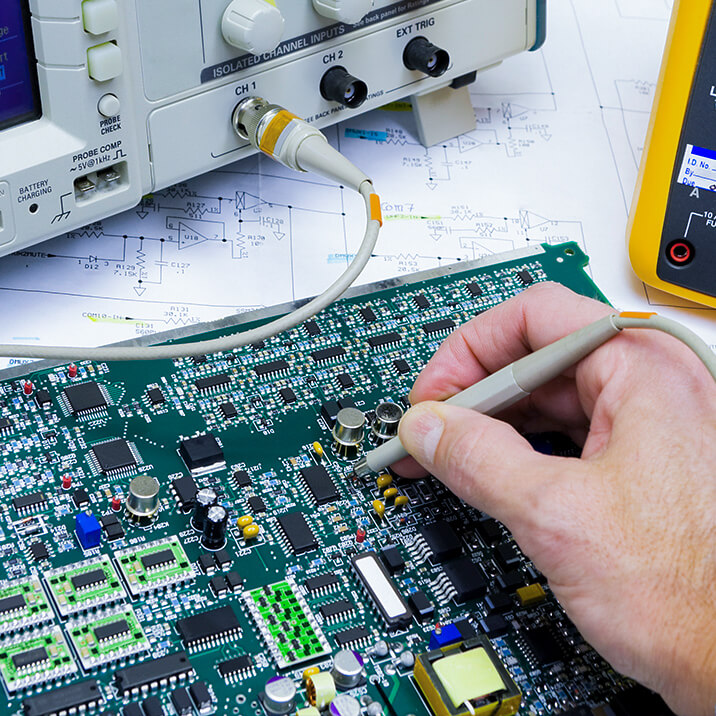

FPGA Verification

Configuration of IP Cores

CPLD Design

Have an idea?

SUBMIT A PROJECT

Our projects

Awards

Why choose Integra Sources

Integration

- Adaptation to customers’ management systems

- Integration into customers’ development processes

Flexibility

- Flexibility in development

- Flexibility in communication

Communication

- High level of communication

- Personal account management

- Legal security guarantee

Transparency

- Transparency in development processes

- Customer’s dashboard

- Clear timelines

Industries

LEARN MORE ABOUT THE INDUSTRIES WE WORK WITH

Consumer Electronics

Power Electronics

Extractive Industry & Manufacturing

Healthcare

Logistics & Transportation

Science & Education

Agriculture

Entertainment

Robotics

Our tech stack

Languages

OS

FPGA Families

IDE

ECAD Software

Interfaces

Wireless Technologies

Math and Simulation Tools

Vendors

Testing and certification

Explore our workflow

GO to workflow page

We get acquainted with the concept of the future device and sign a non-disclosure agreement. The team gathers project requirements, studies relevant documents, and analyzes rival products on the market. At this phase, a preliminary project evaluation is made.

We contact the customer to confirm the project requirements. Then we create a technical specification and set a budget and deadlines.

We make the final evaluation of the project, make up a team, and schedule its workload.

We sign a contract for FPGA or CPLD design. The team gets to work.

There are two possible options. One is to use a devkit to program an FPGA/CPLD first and then design a suitable printed circuit board for it. The other option is to design a PCB with a powerful enough FPGA/CPLD and then program it. After that, the team either leaves the prototype unchanged or replaces the FPGA/CPLD with a less expensive alternative.

The team tests all the functions of the device. We check its performance under corresponding operating conditions and run some tests required for product certification. If necessary, the product is then modified.

After the tests, we finalize the documentation necessary for mass manufacturing, including the bill of materials, Gerber files, etc. We can also prepare manuals if the product is designed for in-house use.

When the development process is finished, customers can enjoy a free warranty period. During this time, the team will fix any bugs and defects in the product.

Reviews

Frequently Asked Questions

What do I get when the project is finished?

Do you do receipt inspections of the components you receive?

What about intellectual property rights?

What IP cores do you use?

Do you validate FPGA firmware?

What FPGA chips do you work with?

Have you worked with SoC systems that use both FPGA and CPU?

What is the main difference between ASIC and FPGA?

Could you help me choose an FPGA chip for my project?

Can you design a custom board for an FPGA?

Will you test my device?

Can you guarantee the quality of the product?

Can you help me with certification?

What is the minimum completion time?

Can you help me with enclosure design?

Who are your customers?